# Mostly Online Project-Based Learning During the COVID-19 Pandemic

**NESTERN SYDNEY**

UNIVERSITY

Matthew D'Souza<sup>a</sup>, Arash Khatamianfar<sup>b</sup>, and Chamith Wijenayake<sup>a</sup> School of Information Technology and Electrical Engineering, University of Queensland, Brisbane, Australia<sup>a</sup> School of Electrical Engineering and Telecommunications, University of New South Wales, Sydney, Australia<sup>b</sup> Corresponding Author Email: c.wijenayake@uq.edu.au

## ABSTRACT

## CONTEXT

Project based learning (PBL) has been used across many Engineering disciplines to successfully deliver courses to achieve better integration and blending of hands-on laboratory components with student learning; increased emphasis on applying the theoretical know how with practical problem solving; and integration of research with undergraduate teaching. During sudden transition to fully online teaching, courses having PBL components have been adversely affected. Some of the challenges included very limited or no access to laboratory resources, lack of opportunities for team-based projects and peer learning, limited interaction between students and teaching staff and poor student engagement. Therefore, successful delivery of PBL related courses in fully online or hybrid mode teaching requires a tailored approach. Experience sharing from successful examples of mostly online PBL teaching will therefore be beneficial for the broader educational community.

## PURPOSE OR GOAL

In this paper, we share our experiences and lessons learnt in delivering Electrical Engineering courses having strong PBL components in two universities in Australia during the COVID-19 pandemic. To this end, we share the course details while outlining aims of using PBL in the courses, descriptions of PBL activities, methodologies and tools used to successfully deliver them during mostly online teaching.

## APPROACH OR METHODOLOGY/METHODS

Approaches used to overcome the challenges and successful delivery of PBL based courses during the pandemic included at-home labs with student acquired hardware, realistic simulations with integration of research and teaching, remote connections, and manipulation of hardware. The paper discusses application of these approaches in three representative courses and draw conclusions of their suitability in mostly online PBL.

## ACTUAL OR ANTICIPATED OUTCOMES

The paper will provide a qualitative comparison of several teaching and learning approaches used to overcome specific challenges in PBL during the mostly online teaching in the pandemic. The paper will provide specific examples and details of the approaches listed above and provide a qualitative comparison.

#### CONCLUSIONS/RECOMMENDATIONS/SUMMARY

Through experience sharing of successful implementations of PBL during the pandemic, the paper will provide insights to develop tailored approaches for mostly online delivery of Electrical and Computer Engineering courses having strong PBL components.

#### **KEYWORDS**

Project based learning, blended learning, integration of research and teaching

# Introduction

Project based learning (PBL) has been used across many Engineering disciplines to successfully deliver courses to achieve: better integration and blending of hands-on laboratory components with student learning; increased emphasis on applying the theoretical know how with practical problem solving; and integration of research related topics with undergraduate teaching (D. Andone and M. Frydenberg 2021, M. Huang and R. Yang 2021, M. Varas-Contreras et. al. 2021, R. C. Panicker and D. John 2021). Fundamental courses in early years of circuits and systems (CAS) curriculum involve standard lectures, guided labs and tutorial and problem-solving sessions to establish the core concepts, while CAS courses in the later years of the curriculum can strongly benefit from PBL. However, organisation and successful delivery of such PBL courses in CAS have been greatly challenged by numerous constraints imposed by the COVID-19 pandemic, mainly due to mostly online teaching with very limited access to laboratory resources, lack of opportunities for team-based projects and peer learning, limited interaction between students and teaching staff and poor student engagement.

In this paper, we share our experience and lessons learnt in delivering CAS courses having strong PBL components in two universities in Australia during the COVID-19 pandemic. To this end, we share the course details while outlining aims of using PBL in the courses, descriptions of PBL activities, methodologies used to successfully deliver them during the pandemic, specific challenges encountered, and approaches taken to overcome them.

# Advanced Embedded System Design Course with PBL

The Advanced Embedded Systems course at university of Queensland is primarily a PBL course that is used for teaching Embedded RTOS (Real Time Operating System), embedded systems hardware and software frameworks in the 4<sup>th</sup> year of Engineering degree. Principles and practice of using wireless communications protocols (e.g. Bluetooth Low Energy), sensor fusion (e.g. Kalman filtering) and machine learning are also introduced. The lectures are given by guest lecturers from industry, who lecture on relevant topics such as RTOS, wireless communications, machine learning and sensor fusion, thus providing increased industrial exposure within the course. During the pandemic, lectures were conducted on Zoom.

## At-Home Labs for Hands-on Work

The course was offered in two modes, catering for both in-person and online students. For inperson students a hardware kit containing wireless development board and sensors was loaned. Online students were required to purchase the kit components from approved vendors and example online links were provided. During 2021 and 2022, all online students were able acquire their own hardware items and conduct hands-on lab work at home.

The course was structured around four lab assignments, a final project, and a final exam. The lab assignments had a strong PBL component and was managed through Zoom consultation sessions by tutoring staff with students completing the project activities at home or on campus. The lab assignments consisted of hardware design, wiring and firmware driver code writing. Typical project-based lab activities included programming with RTOS, working with web dashboards, implementing high-level algorithms and protocols to solve a particular problem such localisation, thus equipping students with components required for the later project. The lab assignments were assessed via online demonstrations. Code and documentation repositories were also used to assess the work offline.

## Online Tools for Labs – Blended learning via H5P

It was required to provide additional blended learning resources for at-home project-based labs. In addition to online lectures and other reading material, a rich set of asynchronous learning modules developed through H5P tools were used (https://h5p.org/). H5P allowed easy development and deployment of interactive web content including interactive workbooks and formative assessments.

As show in figure 1, such blended learning resources for a lab consists of introductory and in-depth content sections, and a quiz (not assessed). The quiz was used to provide feedback to the student on concepts covered in the lab module. The use of H5P based interactive and asynchronous resources had a positive impact on student engagement during mostly online project-based lab activities and was positively received by students.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Memory Mapp          | 1/9                                                                                                                    | <                                                            | >        | 20    |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|-------|------|

| Image: A constraint of the state of the                           | Lab 2.1 Memory Mappe | Prerequiste Labs                                                                                                       |                                                              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Memory Mapped IO O   | The following should be completed before attempting this lab:<br>1. Lab 1.3 C Bitwise Operations                       |                                                              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interfacing Periph O | 1. Lub 1.0 0 Ditmise Operation                                                                                         |                                                              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Peripheral Regist O  | Background<br>The STM32F4/L4 is a Cortex M4 32-bit processor with RAM and Flash memory. The STM32F4/L4 peripherals may |                                                              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Memory Map of P O    | include GPIO, Timers, I2C, SPI                                                                                         | I, USART, ADC, USB, DMA and Ethernet peripherals.            |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Peripheral Regist O  | Key Points Summary                                                                                                     |                                                              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C Programming O      |                                                                                                                        | the memory address space of the microprocessor.              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Exercises O          | <ul> <li>Registers are accessed as</li> </ul>                                                                          |                                                              |          |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | References O         |                                                                                                                        | ccessed via a c struct with the BASE_REGISTER_ADDRESS as the | starting | ) men | nory |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 🗑 Summary & submit   |                                                                                                                        | d to manipulate the individual bits of the register          |          |       |      |

| Lab module start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | Introdu                                                                                                                | ictory content                                               |          |       | -    |

| Interfacing Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2/9 < > ×            | = Exercises                                                                                                            | 7/9                                                          | <        | >     | ×    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | Lab 2.1 Memory Mappe Which                                                                                             | ch register bits are being set by the following?             |          |       |      |

| Lab 2.1 Memory Mappe<br>Interfacing Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | Memory Mapped IO                                                                                                       | ine P_RA 3                                                   |          |       |      |

| Memory Mapped IO  Port-mapped I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | Interfacing Perioh                                                                                                     | ine P_RB 4                                                   |          |       |      |

| Interfacing Periph O Use special CPU instructions: Special_instruction Reg, Port Memory-mapped I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | Peripheral Regist O                                                                                                    | AI= (1 << P_RAI 1 << P_RB)                                   |          |       |      |

| Peripheral Regist O  A simpler and more convenient way to interface I/O devices Each device registers is assigned to a memory address in the address space of the microencestor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | Memory Map of P O                                                                                                      | Bits 2 and 5                                                 |          |       |      |

| Memory Map of P O + Use native CPU load/store instructions: LDR/STR Reg. [Reg. #inm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |                                                                                                                        | Bits 2 and 1                                                 |          |       |      |

| Peripheral Regist O 0x48000020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | C Programming                                                                                                          | Bits 3 and 0                                                 |          |       |      |

| C Programming   Core  Core  STR  0x4809091C  Core  STR  0x4809091R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | The purport          | • Exercises O O I                                                                                                      | Bits 3 and 4                                                 |          |       |      |

| Exercises     O     Attagent of the second of the sec | GPIO                 |                                                                                                                        | bits a and 4                                                 |          |       |      |

| 8x48080018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output               |                                                                                                                        | Check                                                        |          |       |      |

| Bx38000310 Memory Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output               | Check Bits                                                                                                             |                                                              |          |       |      |

In-depth content

↑ Interfacing Peripherals

Quiz

#define BIT\_MASK 1 >> 6 | 1 >> 5

#define BIT\_MASK 0x60

#### Figure 1: Lab Module implemented with asynchronous and interactive H5P Workbook.

2/9 < >

The final project was organised as a group project, with four students assigned per group. Students could choose which groups to join. Each group would choose from a list of topics that covered environmental sensing to indoor sensing. Each group was assessed according to the following criteria, shown in figure 2. The criteria ensures that key principles introduced in the lectures and labs are followed, such as sensor fusion, RTOS and wireless networking. The students were assessed in a final demonstration with a poster presentation. Each group was encouraged to deploy their solution, before the deadline, so that they could show continuous operation for a period of time.

#### **Online Code Repository and Wiki**

Each group used an online code repository and wiki, such as Github to organise and store their project implementation code and to document progress. The wiki was used to document the project, which included a progress (e.g. photos) and various implementation details. The use of repository and wiki features such as issues and milestones, allowed all group members and teaching staff to access and monitor the group's progress during mostly online teaching and to communicate or record any problems or challenges that occurred.

Figure 2: Evaluation criteria for PBL group work.

## **Example Project 1: Methane Chamber Capture Group Project**

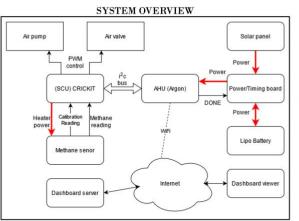

An example project was the Methane Capture Chamber project, as seen in Figure 3. This project involved designing the hardware and software of a methane capture chamber, to measure the methane gas output of a lake water body. A floating platform had to be designed, to operate autonomously and on solar power. The methane sensor information had to be transmitted via a Wifi connection to a web dashboard. This project has been successfully running for 6 months, with the student group awarded a prize by the school for innovation.

#### **Example Project 2: UWB Localisation Group Project**

Another example project was the Ultra-Wide-Band (UWB) Localisation project, as seen in Figure 4. This project involved deploying a network of 12 UWB nodes for high accuracy localisation and tracking with in a confined space of a 5m by 10m. A localisation algorithm using Time of Arrival and Kalman filtering was developed. The group was able to successfully track a user, indoors, within 0.8m.

# Greenhouse gas monitoring using a Capture Chamber

#### KPI'S

- The device can measure methane 1. with a sufficient accuracy

- 2. Able to detect unsafe methane levels and vent the chamber

- 3. Device can connect to a WiFi network and send protocol buffer encoded sensor readings to the Dashboard using MQTT.

- 4. Capable of running for a minimum of one day using the onboard battery and solar panel

- 5. The device can enter low power mode while not taking measurements

#### CHALLENGES

Problem: WiFi would sometimes fail to connect if the signal was poor. Solution: Attempt connection multiple

Problem: No Zephyr library for interfacing with the CRICKIT board. Solution: Port Adafruit C++ sees library to Zephyr (uses same i2c messaging protocol) and wrote drivers for the CRICKIT.

Problem: Excessive power usage running board and sensor continuously. Solution: Periodically power on the system using a low power timer IC.

Capture chamber deployed during the day CONCLUSIONS

- Device measured methane concentration to a good level of accuracy and consistency.

- Successfully vented the chamber at 750ppm. Concentration did not return to zero as the pump is too small, but it is sufficient to avoid dangerous methane concentrations

- Data was successfully sent to an online dashboard using protocol buffer encoding and MQTT over a WiFi connection.

- Measurement interval was set to 10 minutes for testing. The battery lasted for ~12 hours over night starting with 75% charge. For deployment measurements will be taken once per hour which will result in > 24 hours up-time.

- The device powered on at the chosen intervals, then powered off after measurements were taken and sent over WiFi.

#### Figure 3: Example project that created a Methane Gas Emissions Monitoring System for a Lake.

Node Synchronization

\$2

Master controls the radio activity on the

slaves by using TDMA for slave radio to be active only in the time allocated (Avoids UWB

(x,y)

1

(x,0)

Implementation

broadcast overlap).

Operations Overview

#### ULTRA WIDE-BAND (UWB) AND BLUETOOTH AUGMENTED INDOOR LOCALIZATION NETWORK

#### Overview

This project involves developing a network of UWB/Bluetooth (DWM1001C) transceivers to Track multiple people, across a few rooms in GP South. The aim is to minimize the number of nodes required to provide sufficient tracking of a moving target (tag).

This will be achieved by using a BLE mesh network containing advertising nodes, relays and a base station. The base station will receive the "flood" of information from the mesh network, process it and display it to an online dashboard (2D - map).

#### Key Performance Indicators

- Localisation accuracy: Use UWB to localise tags to a fine grain ranging accuracy of at least 0.8m.

- Minimizing static nodes: Use 6 nodes to accurately localize a tag.

Persistent BLE Mesh provisioning: Once provisioned, the nodes remembers their association to the BLE mesh network.

Scalability: The node network should be able to track multiple tags throughout the test area.

Web-Dashboard: Location of tags able to be seen on web dashboard in close to real time.

#### System Overview (Core Technologies)

- Localization using reverse time difference of arrival (RTDOA). Node synchronization using time division

- multiple access (TDMA) and clock calibration packet service (CCP). Ranging calculation used to locate tags

- Data relay using BLE mesh network.

#### **RTDOA Implementation**

#### BLE Mesh Implementation

# **Results Achieved**

- Localisation accuracy: 0.8-1m of ranging accuracy

- Static nodes required:

- Ranging can be done with a minimum of 3 nodes.

- Persistent BLE Mesh:

- Mesh only requires to be provisioned once. PC Interface:

Conclusion

- Dynamically adaptable to custom grid sizes. Tags Tracked:

- · No theoretical max for the number of tags that can be tracked (RTDOA).

- Web Dashboard:

- Tag location updated on dashboard approximately every 600ms.

#### Limitations

- **BLE Mesh Bottleneck:** The mesh has a cap on the amount of data that can be transferred without implementing segmented data messages. This limits the numbers of tags that can be

- active at once. Scalability:

- The maximum grid size is limited by the masters UWB range (Required for TDMA).

#### Improvements

- · Time synchronisation with BLE Mesh Segmented data messages BLE Mesh

- (Increase packet transfer) Implement PC interface to display tag

- location (in real time)

Figure 4: Example Project that created an Indoor Person Tracker using Ultrawide Band Localisation.

Proceedings of AAEE 2022 Western Sydney University, Sydney, Australia, Copyright © Matthew D'Souza, Arash Khatamianfar, and Chamith Wijenayake, 2022.

# **Digital System Design Course**

The digital system design course at university of Queensland was a 4<sup>th</sup> year Engineering core course focusing on hardware description languages and digital design on field programmable gate array (FPGA) based platforms. While this course employed standard lectures and design-oriented lab activities, an attempt was made to integrate research with undergraduate education via PBL, which has been successfully received by students. The course was offered for both in-person and online cohorts of students, mainly relying on Zoom lectures and Zoom based lab classes with remotely access lab computers via remote desktop connections.

During the 13-week semester students completed 5 lab tasks which are semi-guided. Labs were conducted in both in-person (with some interruptions due to campus closure) and online and were mostly simulation based. Students used Xilinx Vivado design environment to design and simulate various combinational and sequential digital blocks followed by finite state machines and controller-data path designs. During the mostly online teaching, students accessed lab computers via remote desktop connections and also used their own computers to run the functional and post-synthesis simulations. For each lab task, students submitted a detailed lab report, and a separate oral assessment was also conducted either on Zoom or in-person. Identity verified oral assessments were used as a remedy for increased academic integrity issues during the pandemic. Teaching staff conducted the oral assessments in the form quick technical interviews, thus providing students an opportunity to improve their verbal communication skills in addition to report writing.

Following the semi-guided lab activities which were mainly based on RTL descriptions using HDL based approach a design project was introduced during weeks 10-13 of the semester with the following objectives: introduce some of the high-level synthesis and model-based system design approaches used in FPGA based system design; integrate research with undergraduate teaching via a tailored project having a research flavour; suitable to be completed and assessed via mostly online simulation based approach, yet challenging and engaging. The project involved design and simulation of a hardware accelerator for a wideband digital beamforming algorithm using Xilinx Model Composer tool flow which integrates Matlab/Simulink and Xilinx Vivado tools to allow rapid prototyping of digital signal processing (DSP) algorithms. This involved the design of parallel hardware accelerated architectures for two-dimensional (2D) finite impulse response (FIR) and infinite impulse response (IIR) filters and optimising the design for FPGA resources and timing constraints. Such topics are typically encountered in master's level research and often require reading published literature. Thus, the effort was to integrate such topics with undergraduate teaching via PBL using suitable projects for simulation based online mode of delivery.

With sufficient guidance provided by teaching staff, students were required to do their own research first to transform their knowledge of one-dimensional filter implementation on an FPGA to obtain parallel hardware architectures suitable for 2D FIR and 2D IIR filters. Teaching staff provided broader context to the project using realistic Matlab simulations and interactive tutorial discussions during online lab classes. Subsequently, a set of design steps are provided to guide students through an iterative design process where an initial design is iteratively optimised to meet certain timing and area constraints. Students had to adapt some of the pipelining and parallel processing techniques they learnt for 1D filters to 2D filters and also optimise for the effects of fixed-point finite precision word lengths within their designs. Finally, students were assessed based on a final report and their design files submitted via the learning management system.

The use of research related project suitable for simulation-based approach in a PBL context was well received by students as evident by some of the student feedback quoted below.

"Interesting and enjoyable practical work. Project was practical, relevant, and had real-life applications"

"I really liked the subject material, and the lectures were interesting and well structured. Even though the pracs were all conducted in the form of simulations, they were still engaging, informative, and a reasonable level of difficulty"

# **Engineering Design Course with PBL**

This course is a 4th-year core course at University of New South Wales, which is aimed at ensuring electrical engineering graduates have accomplished a minimum level of individual proficiency in core disciplines of Electronics, Signal Processing and Control Systems, and group-work skills in a fourth elective topic. All formal lab sessions are assessment opportunities. Students are challenged through a sequence of design tasks in each core topic, while in the fourth elective topic, they will form groups of up to 4 to work on a more comprehensive design task to expose them to a healthy balance between teamwork and individual responsibility. During the COVID-19 pandemic, everything had to be shifted to cater for online delivery while trying to preserve the crucial aspects of the learning outcomes. The main objective in this transition was to ensure that the new project tasks would encompass most of the practical aspects of a real-world project that they would have otherwise been able to encounter and work with in a face-to-face mode. It was also important to maintain the integrity of the assessments around the project and its alignment with the course learning outcomes.

The tasks were converted into simulation-based design challenges. For instance, the Electronics design tasks were required to be completed in the LTspice software with an attached component for preparing a Printed Circuit Board (PCB) for each of the final designs. The tasks themselves were derived from different components of a biomedical device developed by a start-up company. Enforcing the PCB design for each LTspice simulation would ensure that students can gain the practical skills on realising a circuit design into a final prototype ready for manufacturing.

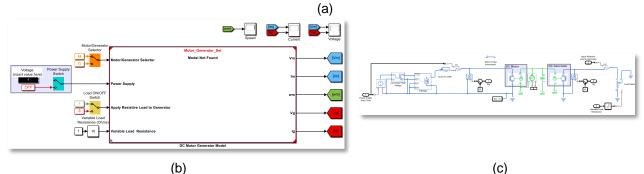

For the Control Systems topic as another example, a realistic virtual model of an actual device was created in MATLAB/Simulink software. For these set of design challenges, a detailed physical model of a DC motor-generator setup (Figure 5(a)) was derived in the lab using empirical data, including estimation of nonlinear friction. To ensure that students can treat this model like an actual device in the virtual mode, the identified parameters were randomised for each student around an acceptable tolerance. These parameters were then used to create a virtual 'black box' model for each student by embedding them in a 'protected model' in Simulink as shown in Figure 5(b) and 5(c). This means each student would have their own individual system without knowing the physical parameters. The students were then able to conduct the virtual experiments to perform system identification as part of the process modelling and designing a control system for their own model based on the project description in that virtual environment.

# Figure 5: (a) The DC motor-generator used to create the virtual model, (b) The protected Simulink model of the device with embedded randomised parameter, (c) Detailed physical implementation of the actual device inside the protected model.

The course was delivered fully online through Microsoft (MS) Teams as the learning management system (LMS). There were two 3-hour lab sessions every week, with 1 lab demonstrator per 8 students for a class of 120 students. An on-demand queuing dashboard system was developed

Proceedings of AAEE 2022 Western Sydney University, Sydney, Australia, Copyright © Matthew D'Souza, Arash Khatamianfar, and Chamith Wijenayake, 2022.

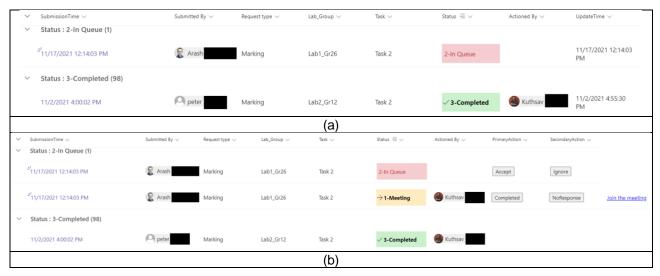

using MS Forms and Power Automate within MS Teams to provide a similar environment where students can engage and communicate with course staff and lab demonstrators. This system allowed students make a request via MS Form in the course channel for general query about the design tasks or ask to get assessed during the scheduled lab time. The queue was updated automatically to show the status of each student request and the lab demonstrator who attended to each request the entire class in the course channel (student view). This system enabled a dedicated MS Teams meeting to be created and sent to the student through Power Automated chat-bot who made the request once an available lab demonstrator accepted the request in the private course staff channel (lab demonstrator view). The student and the lab demonstrator would then join the meeting to either go through the student query or run an assessment. Lab demonstrators, who were trained on online assessment for each design task, would go through checking each requirement of the design task with the student as they share their screen and submit all the files in advance. A major component of the live interview during the meeting was to challenge students with some understanding questions around the design task in addition to checking their results. This was done to ensure that students could demonstrate full understanding of their deliverables and results. The process for this dashboard system is shown in Figure 6.

Figure 6: The online dashboard system, (a) Student view, (b) Lab demonstrator view.

Each core design topic would run for two weeks in a 10-week trimester (total 6 weeks). The groupwork section of the course ran in a similar fashion in the last 3 weeks (with Week 6 as term break). A lab demonstrator would be assigned as a mentor for each group to support them during the schedule lab times. Each group would prepare a short presentation every week as a progress review to be assessed during a live MS Teams meeting by their mentor. The final assessment of the teamwork design task was conducted at the end of the term.

Every stage of this transition into virtual mode was communicated to students with clear expectations. Extra support and feedback were offered on their performance along the way during lockdown through Student Forum and weekly consultation meetings which were recorded for those who would not be able to attend.

# Analysis, Discussion and Conclusions